TSMCの3nm歩留まり率が55%に、それがAppleのチップ生産に何を意味するか

TSMCの3nmプロセスの歩留まり率

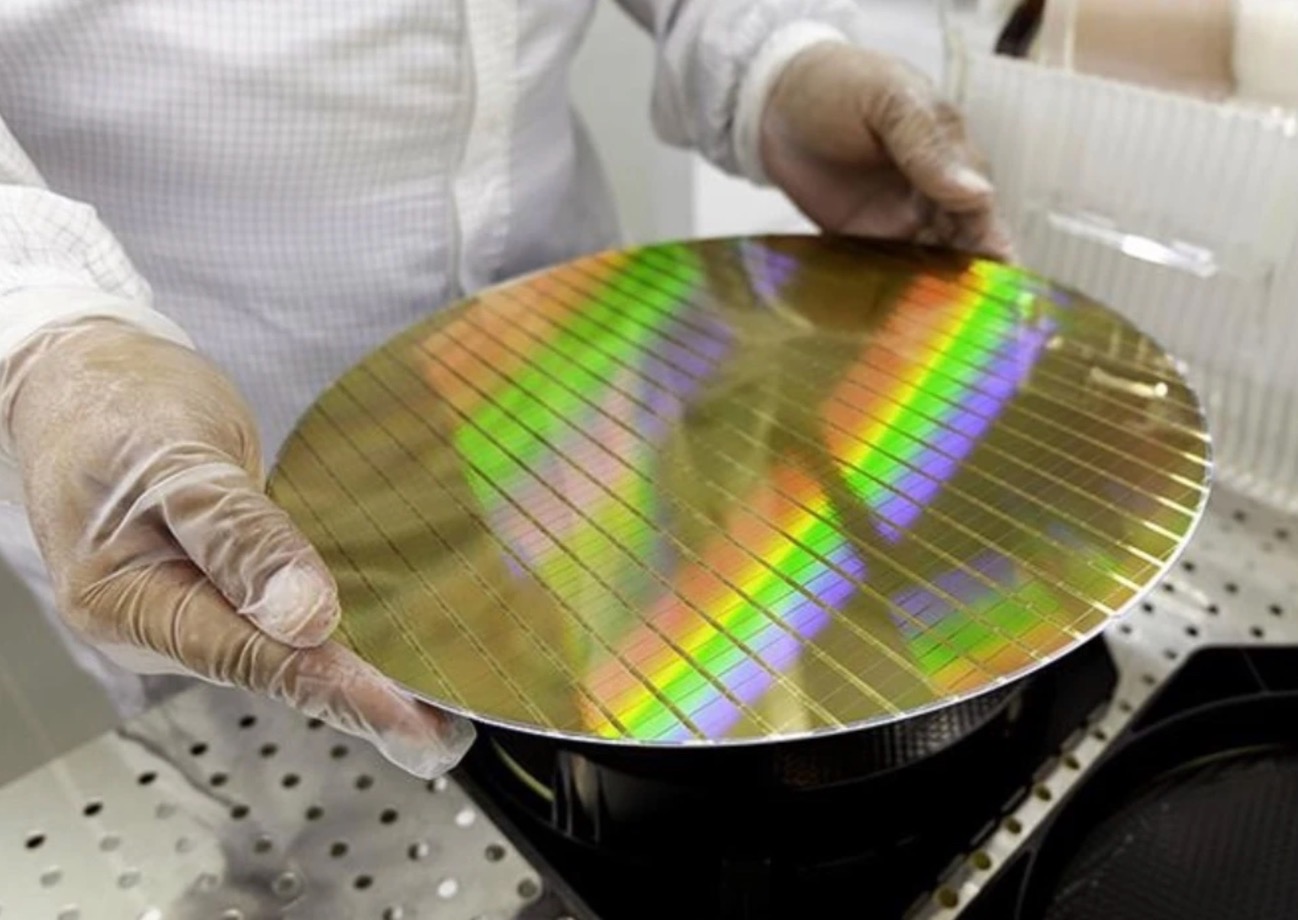

半導体業界は常に進化し続けており、その最前線に立つのが台湾のTSMCです、最近、TSMCの3nmプロセスの歩留まり率が55%に達したと報じられました

これは、生産されるシリコンウェハーの約半分がAppleのA17 BionicとM3チップの製造に使用されることを意味します、しかし、この高価なウェハーの価格のため、今年はiPhone 15 ProとiPhone 15 Pro Maxのみが3nmチップセットを搭載するスマートフォンとなります

AppleとTSMCの特別な取引

AppleはTSMCと特別な取引を結び、良品ダイのみを支払うことでウェハーの価格を抑えています、しかし、Arete ResearchのシニアアナリストであるBrett Simpson氏は、歩留まり率が70%に達した時点で、TSMCは最も収益性の高いクライアントを標準のウェハー価格に戻すと述べています

Simpson氏は、「私たちは、TSMCが2024年の前半にAppleとともにN3の通常のウェハー基準の価格に移行すると考えています。現在、A17とM3プロセッサのTSMCでのN3の歩留まり率は約55%(この段階のN3開発では健全なレベル)で、TSMCは各四半期に歩留まり率を約5ポイント以上向上させる予定です」と述べています

3nmプロセスの現状と未来

A17 Bionicは82のマスク層を必要とし、ダイサイズが100-110平方mmの範囲にあるため、各ウェハーは620個のチップを生産できます

これに対して、M3チップは135-150mm平方のダイサイズで、ウェハーあたり最大450個のチップを生産できます

TSMCの初代3nmチップは、A17 BionicのためのN3Bプロセスノードを使用しています、2024年には、Appleは生産コストが低く、歩留まり率が高いN3Eノードに切り替える可能性があります

ただし、一部の情報提供者によれば、N3EノードはN3Bノードに比べて性能向上が少ないとのことです

TSMCとSamsungの競争

TSMCとSamsung Foundryの間の競争について、Susquehanna International GroupのシニアエクイティリサーチアナリストであるMehdi Hosseini氏は、TSMCが引き続き優位に立っていると述べています

「私たちの見解では、Samsung Foundryが安定した先端プロセス技術をまだ示していない一方で、IFS(Intel Foundry Services)は競争力のあるソリューションを提供するまでに数年かかるため、TSMCは先端ノードの選択肢として優れています」と彼は述べています

未来への展望

TSMCは、2025年にN2プロセスの生産を開始すると発表しています

TSMCのWei氏は、「N2では、顧客の関心とエンゲージメントが高いことを観察しています。当社の2nm技術は、導入時に業界で最も先進的な半導体技術となり、密度とエネルギー効率の両方で最高となり、当社の技術リーダーシップをさらに未来へと延ばします」と述べています

(Via Phone Arena.)

LEAVE A REPLY